|

|

МЕНЮФестивали и конкурсы Семинары Издания О МОДНТ Приглашения Поздравляем НАУЧНЫЕ РАБОТЫ |

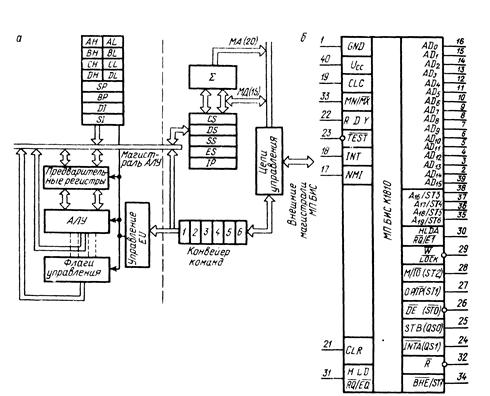

Реферат: Методические указания по микропроцессорным системамКонтрольные вопросы1. Поясните понятия модульности, магистральности и микропрограммируемости МПС при проектировании. 2. Перечислите задачи, решаемые разработчиками при проектировании МПС. 3. Перечислите основные этапы проектирования МПС. 4. Назовите концептуальные уровни описания МПС при проектировании и разработке. 5. Перечислить основные методы контроля правильности проектирования МПС. 6. Какими свойствами должна обладать проектируемая МПС для выполнения этапа ее отладки? 7. Перечислите виды неисправности при проектировании МПС. 8. Назовите причины физической и субъективной неисправностей МПС. 9. Поясните понятия: диагностика неисправности, отладка. 4. ОРГАНИЗАЦИЯ И ОСОБЕННОСТИ ПРОЕКТИРОВАНИЯ МПС НА ОСНОВЕ ОДНОКРИСТАЛЬНЫХ МИКРОЭВМ4.1. Общие принципы организации однокристальных микроЭВМС повышением степени интеграции микросхем стало возможным реализовать на одном кристалле сложные функциональные блоки. Зa недолгую историю развития элементной базы микропроцессорных вычислительных устройств были разработаны принципиально новые структуры БИС. Такие микросхемы, имеющие высокую степень интеграции и работающие согласно заданной программе, получили название микропроцессорных БИС (МП БИС). Стало возможным реализовать ЭВМ на нескольких типах МП БИС, объединенных в так называемые микропроцессорные комплекты (МПК) БИС, которые отличаются друг от друга функциональными возможностями, технологией изготовления, конструктивными особенностями, быстродействием, потребляемой мощностью и т.п. Микропроцессорные БИС принято разделять на три основных класса: секционированные с наращиванием разрядности и микропрограммным управлением; модульные МП - на основе однокристальных МП БИС с фиксированным набором команд и разрядностью; однокристальные микроЭВМ. Секционированные МП БИС включают совместимые микросхемы различного функционального назначения, на основе которых можно реализовать MПC различной структуры и разрядности, кратной разрядности секции. В зависимости от назначения разрабатываемой аппаратуры выбирается структура секционированных БИС и система команд. Эти БИС широко применяются при проектировании высокопроизводительных мультимикропроцессорных систем. МП БИС на основе однокристальных МП и однокристальных микроЭВМ, обладающие меньшей производительностью, но гибкой системой команд и большими функциональными возможностями, ориентированы на широкое применение в различных областях науки, техники и производства - от контроллеров и калькуляторов, до МПС управления, цифровой обработки сигналов и интеллектуальных робототехнических систем. В настоящее время наибольшее распространение получили МП БИС на основе разновидностей МОП- технологии и интегральной инжекционной логики(И2Л). Требования к быстродействию предопределили развитие биполярных МП БИС на основе транзисторно-транзисторной логики с диодами Шотки(ТТЛШ) и эмиттерно-связанной логики (ЭСЛ). Следует отметить, что при проектировании МПС для различных применений обязательным условием эффективного использования МП БИС является конструктивная и технологическая совместимость всей элементной базы системы - микросхем малой, средней и большой степени интеграции, используемых в центральном процессоре, блоках памяти, устройствах ввода-вывода. Как правило, в состав однокристальных МП БИС, служащих для реализации однокристальных микроЭВМ и МПС на их основе, входят следующие БИС: микропроцессор с памятью, последовательный или параллельный интерфейс, контроллеры (ПДП, прерываний, клавиатуры и т.п.). В последние годы получила новое развитие номенклатура однокристальных микроЭВМ и специализированных МПК цифровой обработки сигналов, которые имеют большую перспективу применения в силу своих функциональных возможностей и характеристик. Состав и структура МПК БИС зависят от областей применения и, как правило, имеют минимально необходимое число БИС для организации микроЭВМ и МПС. Типичным представителем МПС с однокристальным МП является отечественный микропроцессорный комплект серии К1810, в котором реализуются и находят дальнейшее развитие идеи построения одно- и многопроцессорных систем на базе МП БИС с фиксированным набором команд. В комплект входят как универсальные и специализированные процессоры (процессор ввода-вывода, арифметический процессор), так и схемы, позволяющие сформировать магистрали микроЭВМ. Комплект может расширяться за счет разработки новых схем, программно и аппаратно совместимых с МП БИС. Основной схемой в комплекте является МП БИС К1810ВМ86, которая представляет собой однокристальный 16-разрядный МП с мультиплексной 20-разрядной магистралью адреса и 16-разрядной магистралью данных и рассчитана на работу как в одно-, так и в многопроцессорных системах. Схема выпускается в 40-выводном корпусе (рис. 5.1). Ряд выводов схемы используется для выдачи импульсов управления, синхронизирующих работу микроЭВМ. Питание схемы осуществляется от источника с напряжением 5 В. Синхронизация работы МП БИС осуществляется импульсами внешнего тактового генератора, подаваемыми на вход CLK. Эффективность работы МП БИС К1810ВМ86 существенно повышена за счет введения команд математических операций (включающих умножение и деление) над 8- и 16-разрядными числами, команд побитовой обработки чисел, команд работы с массивами данных, расширения видов прерываний работы МП БИС, а также реализации конвейерного типа выполнения команд в самой БИС. Микропроцессорная БИС может работать с памятью объемом до 1 Мбайта, обмениваться информацией с 64 Кбайтами внешних устройств, имеет 256 типов различных прерываний. Обычно процесс выполнения команд программы в МП включает в себя следующие этапы: извлечение кода команды (операндов команды, если этого требует код команды) из памяти; выполнение команды; запись результата (если этого требует команда). Как правило, в МП все эти этапы выполняются последовательно, что приводит к недоиспользованию по временной загрузке магистралей микроЭВМ. В МП БИС К1810ВМ86 процесс выполнения команд состоит из тех же этапов, однако проводится в двух раздельных процессорных блоках (см. рис. 4.1, а): блоке выполнения команд (execution unit – EU) и блоке сопряжения с магистралями (Bus Interface Unit – BIU). В функции BIU входит извлечение из памяти кода команд и их операндов, а также запись результата в память. Блоки могут работать независимо друг от друга, и, следовательно, процессы преобразования и передачи информации в них могут идти параллельно. Блок выполнения команд имеет 16-разрядное АЛУ с регистром состояния и флагами управления, а также регистры общего назначения. Все регистры и внутренние магистрали блока 16-разрядные. Блок не имеет связи с внешними магистралями МП БИС. На АЛУ поступают коды команд из конвейера команд, расположенного в BIU. Если в результате дешифрации кода команд в АЛУ необходимо получение одного или нескольких операндов по внешним магистралям МП БИС, то EU запрашивает BIU на получение и размещение необходимых данных в BIU. Несмотря на то, что все адреса, с которыми оперирует EU, 16-разрядные, BIU производит необходимое преобразование адресов так, чтобы EU имел возможность обращаться ко всему возможному адресному пространству (1 Мбайт) микропроцессорной системы.

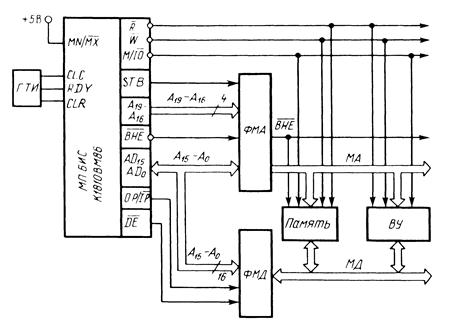

Рис. 4.1. Упрощенная схема МП БИС КР1810 ВМ86 Блок сопряжения с магистралями производит все пересылки данных и кодов для EU. Пересылки между МП БИС и памятью или внешними устройства-ми осуществляются по требованию EU. В то время как EU занят выполнением команды, блок BIU получает последующие в программе коды команд из памяти и сохраняет их в конвейере команд. В конвейере может быть записано до шести кодов команд. Это позволяет BIU выдавать в EU сохраненные команды по мере необходимости без загрузки внешних магистралей МП БИС. Блок BIU организует получение нового кода команды, как только два байта в конвейере команд будут переданы в EU. За один цикл получения кода команды в блок BIU записываются с МД два байта команды. В большинстве случаев в BIU находится хотя бы одна команда и EU не ждет, пока очередная команда будет извлечена из памяти. Коды команд подаются в EU последовательно так, как они записаны в программе. Если EU выполняет команду передачи управления в другое место программы, то BIU очищает конвейер команд, получает код команды из нового адреса, передает его в EU и начинает заполнять конвейер заново. Если EU требует обращения к памяти или внешнему устройству, то BIU приостанавливает процесс получения команд в конвейер и организует необходимый цикл обмена данными. На рис. 4.2 приведен пример построения однопроцессорной системы.

Рис. 4.2. Структура микроЭВМ на базе МП БИС КР1810ВМ86

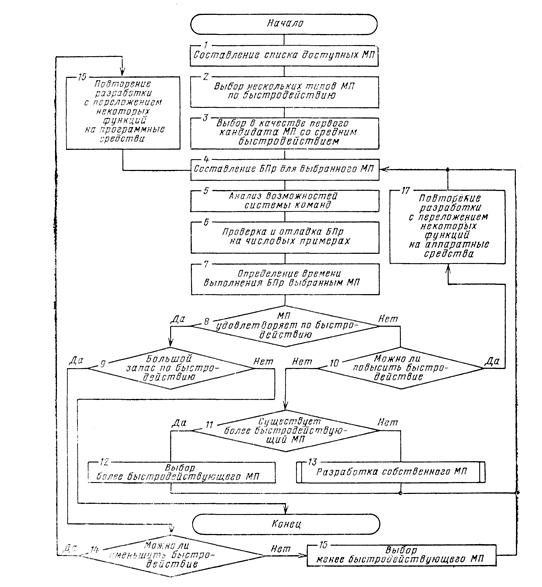

4.2. Особенности проектирования МПC на основе однокристальных микроЭВМ и контроллеров.Так же, как и при выполнении системного этапа проектирования любых ЭВМ, при проектировании МПC на основе однокристальных микроЭВМ с самого начала должны быть определены и документированы основные функциональные характеристики разрабатываемой системы: разработчики и изготовители МПС могут интерпретировать характеристики не так, как заказчик и это может привести к необходимости переделки уже выполненной работы. Результатом этого этапа должна быть структурная схема МПС с определением всех входных и выходных сигналов и их электрических и временных характеристик. На этом же этапе желательно составить так называемый "служебный обзор", в котором форма задания функциональных характеристик заказчика заменяется на более удобную для разработчика. Толкование этого документа должно иметь полное понимание и однозначность. Можно также внести предложения по улучшению характеристик и параметров МПС, которые заинтересуют заказчика. Выбор MП MПC - достаточно сложная процедура, при которой надо учитывать множество факторов. Если, например, доступна только одна модель однокристального МП, то проблема выбора сводится к ответу на вопрос: можно ли построить МПС с требуемыми характеристиками на основе этого МП. При разработке МПС с предполагаемым большим объемом выпуска выбор и проверка правильности принятого решения требуют значительного времени. Так как одним из главных критериев при выборе MП является требуемое быстродействие, наиболее распространенным методом его оценки является использование так называемых б е н ч м а р к о в с к и х программ (БПр). БПр - это программа решения на анализируемом МП такой задачи, которая по составу операций соответствует классу задач предполагаемого применения. Обычно длина БПр – 100-200 команд. В состав ее обязательно должны входить операции по вводу-выводу. Важным достоинством выбора МП на основе БПр является то, что она не только определяет время решения задачи на конкретном MП, но и вскрывает достоинства и недостатки его системы команд для заданной области применений. Если проверка правильности составления БПр на конкретных числовых примерах покажет, что БПр не дает удовлетворительных временных показателей ее выполнения, следует использовать один из следующих подходов: - повторить разработку для этого же МП, но перераспределить при этом программные и аппаратные средства таким образом, чтобы обеспечить требуемые характеристики по быстродействию; - выбрать более быстродействующий МП. Процедура выбора МП с помощью БПр приведена на рис. 4.3. Разработка аппаратной части МПС должна начинаться с разработки ее процессора, поскольку в дальнейшем он может использоваться для проверки других устройств. Обычно в процесс разработки процессора входят этапы по разработке вспомогательного оборудования, которое позволяет упростить проверку и отладку процессора. В состав МПК БИС в ряде случаев не входит генератор тактовых импульсов, поэтому он должен быть разработан и изготовлен в первую очередь, так как он может быть единственным элементом, необходимым для запуска процессора. Если МПС реализуется на сравнительно большом числе ИС, а рабочая программа достаточно сложна, то потребуется разработка и изготовление пульта. Он должен иметь индикацию состояния адресной шины и шины данных. Кнопки и переключатели должны обеспечивать управление пуском и остановкой, шаговым режимом и вводом данных и команд в ОЗУ МПС. Правильность функционирования процессора МПС должна проверяться в режиме выполнения программы. Поскольку платы памяти изготавливаются обычно позже, для проверки процессора необходимо разработать и изготовить макет небольшого ЗУ.

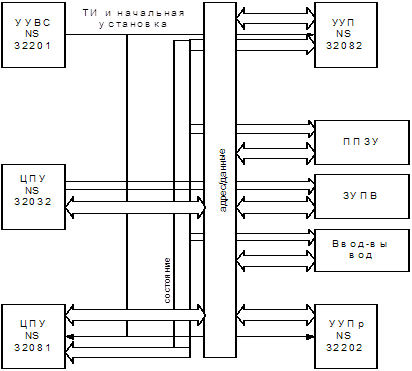

Рис. 4.3. Процедура выбора МП Проверку рекомендуется начать с выполнения команды условного перехода, которая передает управление самой себе. Это позволит, во-первых, убедиться в работоспособности МП, а, во-вторых, исследовать временную диаграмму работы процессора MПС с помощью осциллографа. На основе макета памяти можно проверить выполнение всех команд, а позже проверить работоспособность остальной аппаратуры МПС. Характеристики МПС в значительной степени определяются организацией обмена информацией между МП, основной памятью и внешними устройствами. Поэтому разработка интерфейса системы является одним из наиболее ответственных этапов разработки. Сложностъ этого этапа обуславливается тем, что связь БИС, входящих в MПK, обычно функционально и структурно строго регламентирована руководящим техническим материалом, спецификой МПС, предназначенной для конкретного применения, и определяется исключительно внешними устройствами МПС и их связью с МП и основной памятью. На аппаратуру, обеспечивающую этот интерфейс, в некоторых случаях приходится 60-80% общих аппаратурных затрат. В функции интерфейса обычно входят операции по дешифрации адреса устройства, синхронизации обмена, согласование информационных и управляющих сигналов, дешифрация кода команды, генерирование запросов на прерывание процессора и др. Для того, чтобы МПС могла выполнять задачи обработки данных, ее необходимо снабдить соответствующим программным обеспечением (ПО), которое подразделяется на две части: системное и прикладное. Основой системного ПО служит, как правило, некоторая операционная система, которая включается в состав МПС при ее поставке потребителю. Прикладное ПО содержит комплекс программ, соответствующих специфике области применения системы. И системное, и прикладное ПО создаются с помощью подходящих языков программирования, включая язык Ассемблера данной МПС и языки высокого уровня. Составляя программу для МПС (или микроЭВМ) в машинных кодах или на языке Ассемблера, программист абстрагируется от всего многообразия элементов МПС и имеет дело лишь с системой команд и ограниченным числом ее регистров, называемых программно-доступными регистрами. Эти регистры характеризуются тем, чти их имена или условные обозначения (номера) могут применяться в машинных командах, а содержимое регистров может быть изменено, прочитано или использовано с помощью соответствующих команд по желанию программиста. Программно-доступные регистры обычно составляют лишь небольшую часть всех регистров MП. Никакие другие элементы МП, кроме его программно-доступных регистров, не находят отражения в программах, написанных в кодах системы или на языке Ассемблера. Следовательно, с точки зрения программиста МП МПС представляет собой совокупность программно-доступных регистров, которые каким-то образом связаны с остальными компонентами и элементами процессора с целью выполнения операций, соответствующих системе команд данного МП. Можно, таким образом, полагать, что набор программно-доступных регистров и система команд – это главное, что нужно знать программисту о микропроцессоре, чтобы приступить к написанию программы. 4.3. Обзор перспективных проектов МПС на основе однокристальных комплектов БИСВ данном подразделе рассматриваются проекты МПС, созданные в 80-90х годах и послужившие основой для современных МПС на основе однокристальных МП. В рассматриваемых классах МПС были применены новейшие достижения как технологий, так и новых принципов организации архитектур самих МП и МПС в целом. МПС на основе 32-разрядного МП NS32032 представляет собой результат развития разработок фирмы National Semuiconductor в области МП, для которых характерна 32-разрядная внутренняя архитектура при 8- или16-разрядных шинах данных и интерфейса. Структура МПС на основе МП NS32032 представлена на рис. 4.4.

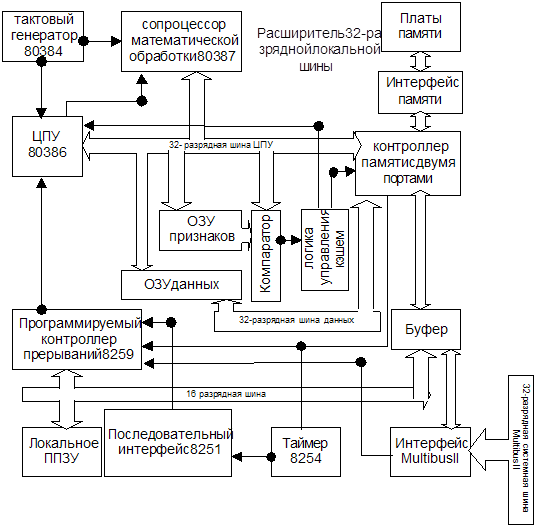

Рис. 4.4. Структура МПС на основе МП NS32032 МПС кроме МП NS32032 содержит следующие вспомогательные микросхемы: - устройство управления временными состояниями(УУВС) NS32201; - устройство управления памятью (УУП) NS32082; - устройство обработки с плавающей запятой (УОПЗ) NS32081; - устройство управления прерываниями (УУПр) NS32202; В отличие от ситуаций с сопроцессорами, которые не способны декодировать свои собственные команды, при работе со вспомогательными процессорами УОПЗ и УУП центральный МП (ЦПУ) декодирует коды операций и останавливается на время пересылки команд и данных в эти процессоры, причем дополнительные строки программы на это не затрачиваются. МПС на основе МП 80386 (рис. 4.5), представляющего собой 32-разрядную версию 16-разрядного МП 80286, содержит также сопроцессор математической обработки 80387, внутриплатную кэш-память с прямым отображением и двух- портовый контроллер памяти, обеспечивающий ЦПУ и системной шине возможность доступа к памяти через расширитель 32-разрядной локальной шины. В данной МПС реализуется обработка данных всех типичных видов (16-и 32-разрядных целых чисел, битовых команд, цепочек байтов, двоично-десятичных чисел), а если в состав системы включен сопроцессор 80387 – обработка 32-, 64- и 80-разрядных действительных чисел.

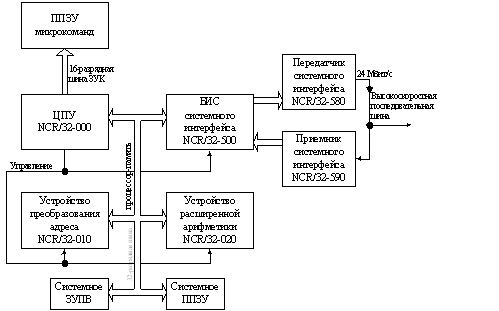

Рис. 4.5. Структура МПС на основе МП 80386 МПС на основе МП NCR/32 (рис. 4.6). Данный МП обладает уникальной способностью, заключающейся в возможности микропрограммного управления им с целью эмуляции набора команд других МП или МПС с использованием внешнего ППЗУ.

|

Приглашения09.12.2013 - 16.12.2013 Международный конкурс хореографического искусства в рамках Международного фестиваля искусств «РОЖДЕСТВЕНСКАЯ АНДОРРА»09.12.2013 - 16.12.2013 Международный конкурс хорового искусства в АНДОРРЕ «РОЖДЕСТВЕНСКАЯ АНДОРРА»

|

Copyright © 2012 г.

При использовании материалов - ссылка на сайт обязательна.